Scratchpad memory (SPM) is considered a useful component in the memory hierarchy, solely or along with caches, for meeting the power and energy constraints as performance ceases to be the sole criteria for processor design. The last phase of the methodology is an exploration approach for energy-aware banking of the on-chip memory, which takes into account both the static and dynamic energy consumption. The system can perform an exploration based on energy consumption of signal assignments to the off- and on-chip memory layers, followed by a storage-efficient mapping of signals to the physical memories.

Scratchpad memory vs cache software#

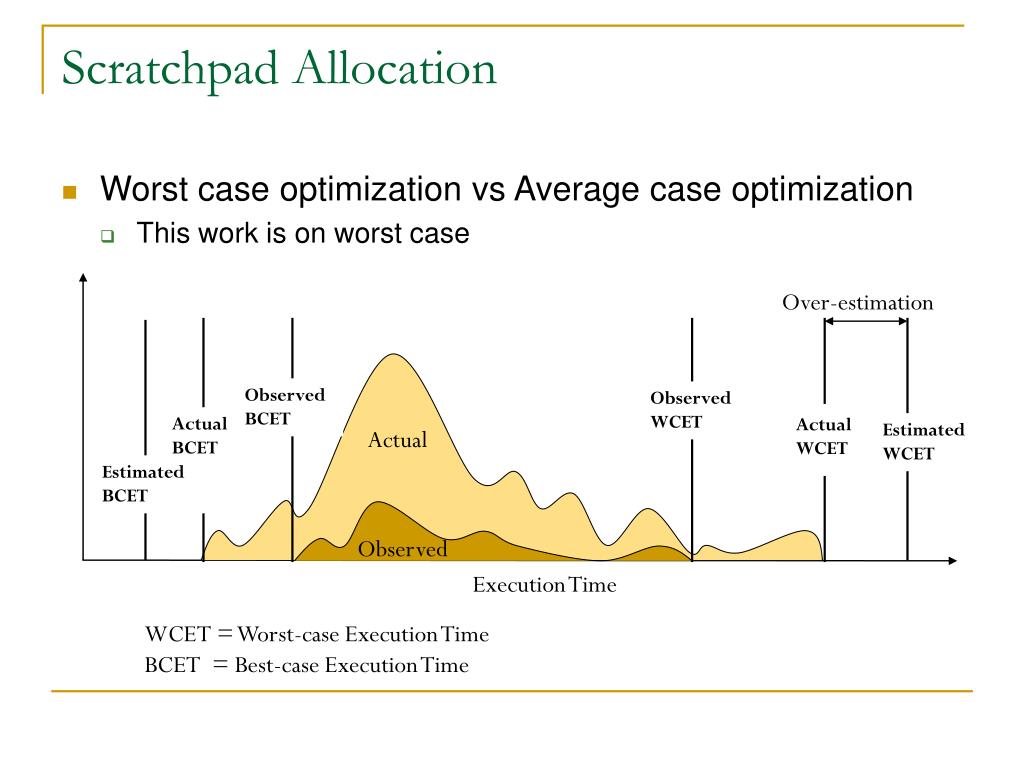

Within this memory management software system, the designer can explore different algorithmic specifications functionally equivalent, by computing their minimum storage requirements. Starting from the high-level behavioral specification of a given application, several memory management tasks are addressed in a common algebraic framework, using data-dependence analysis techniques similar to those used in modern compilers. This paper presents an energy-aware electronic design automation (EDA) methodology for the system-level exploration of hierarchical storage organizations, focusing mainly on data-intensive signal processing applications. It will also make a first step towards making them useful for general purpose multicore processors. The paper not only serves as a collection of recent references, information and classifications for easy comparison and analysis but also as a motivation for improving the SMC management framework for embedded systems. We separate and compare these trends based on general classifications developed during our study. This paper1 analyzes the current trends for optimizing the use of these SMCs. Software can explicitly read and write some or all of the memory references within a block of caches. Software-managed on-chip memories (SMCs) are on-chip caches where On-chip memory system will be the major bottleneck in future processors. For example increasing the clock rate increases the average access time to on-chip caches which in turn lowers the average number of instructions per cycle of the processor. Processors are unable to achieve significant gains in speed using the conventional methods. Our experimental results indicate the strengths and weaknesses of each proposed architecture and the allocation method, which offers interesting on-chip memory design options to enable multicore platforms for hard real-time systems.

The SPM based multicore architectural design and the related allocation methods thus form a comprehensive solution to hard real-time multicore based computing. To support these architectures, we propose the dynamic memory objects allocation based partition, the static allocation based partition, and the static allocation based priority L2 SPM strategy to retain the characteristic of time predictability while attempting to maximize the performance and energy efficiency. To achieve time predictability while minimizing the impact on performance, this paper explores several time-predictable scratch-pad memory (SPM) based architectures for multicore processors. Cache memories, while useful for improving the average-case memory performance, are not time predictable, especially when they are shared in multicore processors. Time predictability is crucial in hard real-time and safety-critical systems.

0 kommentar(er)

0 kommentar(er)